- 您现在的位置:买卖IC网 > Sheet目录3881 > PIC18F4539T-E/ML (Microchip Technology)IC PIC MCU FLASH 12KX16 44QFN

2002 Microchip Technology Inc.

Preliminary

DS30485A-page 279

PIC18FXX39

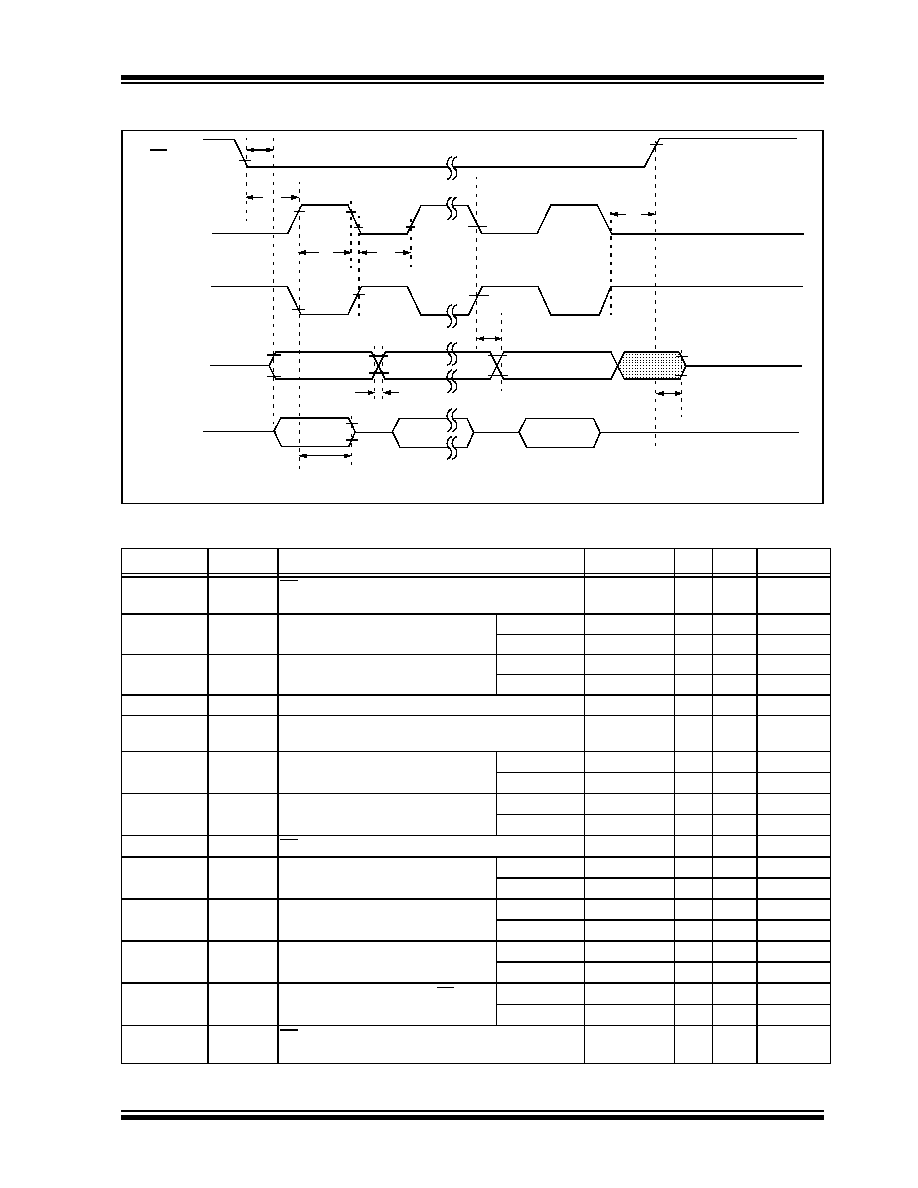

FIGURE 23-15:

EXAMPLE SPI SLAVE MODE TIMING (CKE = 1)

TABLE 23-14: EXAMPLE SPI SLAVE MODE REQUIREMENTS (CKE = 1)

Param. No.

Symbol

Characteristic

Min

Max Units Conditions

70

TssL2scH,

TssL2scL

SS

↓ to SCK↓ or SCK↑ input

TCY

—ns

71

TscH

SCK input high time

(Slave mode)

Continuous

1.25 TCY + 30

—

ns

71A

Single Byte

40

—

ns

(Note 1)

72

TscL

SCK input low time

(Slave mode)

Continuous

1.25 TCY + 30

—

ns

72A

Single Byte

40

—

ns

(Note 1)

73A

TB2B

Last clock edge of Byte 1 to the first clock edge of Byte 2 1.5 TCY + 40

—

ns

(Note 2)

74

TscH2diL,

TscL2diL

Hold time of SDI data input to SCK edge

100

—

ns

75

TdoR

SDO data output rise time

PIC18FXXXX

—

25

ns

PIC18LFXXXX

—

60

ns

VDD = 2V

76

TdoF

SDO data output fall time

PIC18FXXXX

—

25

ns

PIC18LFXXXX

—

60

ns

VDD = 2V

77

TssH2doZ SS

↑ to SDO output hi-impedance

10

50

ns

78

TscR

SCK output rise time (Master mode)

PIC18FXXXX

—

25

ns

PIC18LFXXXX

—

60

ns

VDD = 2V

79

TscF

SCK output fall time (Master mode)

PIC18FXXXX

—

25

ns

PIC18LFXXXX

—

60

ns

VDD = 2V

80

TscH2doV,

TscL2doV

SDO data output valid after SCK

edge

PIC18FXXXX

—

50

ns

PIC18LFXXXX

—

150

ns

VDD = 2V

82

TssL2doV SDO data output valid after SS

↓ edge PIC18FXXXX

—

50

ns

PIC18LFXXXX

—

150

ns

VDD = 2V

83

TscH2ssH,

TscL2ssH

SS

↑ after SCK edge

1.5 TCY + 40

—

ns

Note 1: Requires the use of Parameter # 73A.

2: Only if Parameter # 71A and # 72A are used.

SS

SCK

(CKP = 0)

SCK

(CKP = 1)

SDO

SDI

70

71

72

82

74

75, 76

MSb

bit6 - - - - - -1

LSb

77

MSb In

bit6 - - - -1

LSb In

80

83

Note:

Refer to Figure 23-4 for load conditions.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18LF8680T-I/PT

IC PIC MCU FLASH 32KX16 80TQFP

PIC16F1936-I/SO

IC PIC MCU FLASH 512KX14 28-SOIC

PIC18F24K20-I/SO

IC PIC MCU FLASH 8KX16 28SOIC

PIC18LF8585T-I/PT

IC PIC MCU FLASH 24KX16 80TQFP

XF2J-3024-11

CONN FPC 30POS 0.5MM SMT

PIC18LF6525T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18LF8621T-I/PT

IC PIC MCU FLASH 32KX16 80TQFP

PIC18F8620T-E/PT

IC PIC MCU FLASH 32KX16 80TQFP

相关代理商/技术参数

PIC18F4539T-E/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539T-I/ML

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539T-I/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550EPT

制造商:Microchip Technology Inc 功能描述:

PIC18F4550-I/ML

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550-I/P

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550-I/PT

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550T-I/ML

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT